# User Manual DA16200 H/W Design Guide UM-WI-006

# **UM-WI-006**

# DA16200 H/W Design Guide

# Contents

| Со  | ntents                  | ;          |                                    | 2 |

|-----|-------------------------|------------|------------------------------------|---|

| Fig | jures                   |            |                                    | 3 |

| Ta  | bles                    |            |                                    | 3 |

| Те  | rms ar                  | nd Definit | ions                               | 4 |

| Re  | ferenc                  | es         |                                    | 4 |

| 1   | Introd                  | duction    |                                    | 5 |

| 2   | Sche                    | matic Gui  | idelines                           | 6 |

| _   | 2.1                     |            | ) Power Supply                     |   |

|     |                         | 2.1.1      | Power Management                   | 7 |

|     |                         | 2.1.2      | VBAT                               | 3 |

|     |                         | 2.1.3      | Internal DC/DC                     | 3 |

|     | 2.2                     | RF         |                                    | 9 |

|     |                         | 2.2.1      | Antenna                            | 9 |

|     |                         | 2.2.2      | Antenna information of DA16200 EVK | Э |

|     |                         | 2.2.3      | RF Input Requirement               | I |

|     | 2.3                     | Clock      | 11                                 | I |

|     |                         | 2.3.1      | Main Clock 12                      | I |

|     |                         | 2.3.2      | RTC Clock                          | I |

|     | 2.4                     | Serial Fla | ash 12                             | 2 |

|     |                         | 2.4.1      | Serial Flash Interface             |   |

|     |                         | 2.4.2      | Serial Flash Selection Guide       | 3 |

| 3   | PCB                     | Layout Ex  | xample14                           | 1 |

|     | 3.1                     | Groundin   | ng14                               | 1 |

|     | 3.2                     | PCB Lay    | out Example                        | 5 |

| 4   | Recommended Footprint17 |            |                                    |   |

| Re  | vision                  | History    |                                    | 3 |

# **Figures**

| Figure 1: DA16200 Application Schematic        |

|------------------------------------------------|

| Figure 2: Power Management Block Diagram7      |

| Figure 3: Tested Antenna Dimension             |

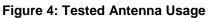

| Figure 4: Tested Antenna Usage                 |

| Figure 5: Tested Antenna Radiation Pattern 10  |

| Figure 6: Serial Flash Application Schematic12 |

| Figure 7: DA16200 Image Structure              |

| Figure 8: Ground vias on PAD14                 |

| Figure 9: PCB Layout Example: Top layer 15     |

| Figure 10: PCB Layout Example: 2nd layer 15    |

| Figure 11: PCB Layout Example: 3rd layer 16    |

| Figure 12: PCB Layout Example: Bottom layer 16 |

| Figure 13: DA16200 Ground Footprint 17         |

# **Tables**

| Table 1 Power Pin Descriptions         | 8    |

|----------------------------------------|------|

| Table 2 Recommended LC filter          |      |

| Table 3 Recommended Serial Flash List  | . 13 |

| Table 4 New Flash verification process | . 13 |

#### **NDA Confidential**

# **Terms and Definitions**

| PCB  | Printed Circuit Board                     |

|------|-------------------------------------------|

| QFN  | Quad Flat No-Leads                        |

| RF   | Radio Frequency                           |

| GPIO | General Purpose In/Out                    |

| DCDC | Direct Current Direct Current             |

| LDO  | Low Drop Out                              |

| RTC  | Real-Time Clock                           |

| SFDP | Serial Flash Discoverable Parameters      |

| QSPI | Quad Serial Peripheral Interface          |

| SPI  | Serial Peripheral Interface               |

| AMBA | Advanced Microcontroller Bus Architecture |

# References

[1] <DA16200>, Datasheet, Dialog Semiconductor.

**User Manual**

# **1** Introduction

This document provides a set of guidelines that help users prepare schematics and PCB layouts for products with the DA16200. Recommended schematic, chip interfaces and surrounding components as well as PCB layout guidelines of both devices are provided.

# 2 Schematic Guidelines

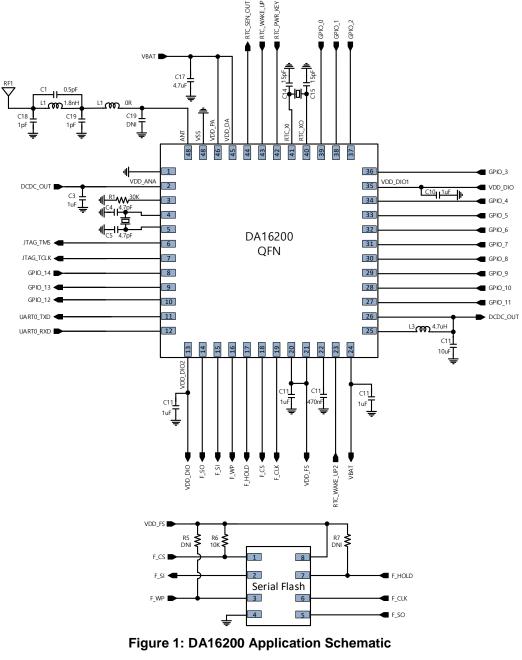

The DA16200 application schematic includes the following five parts:

- Power supply: Digital Power Supply, Analog Power Supply

- RF: Contains antenna part

- Clock: Main Clock, RTC Clock

- Flash interface

- Digital I/O: GPIO pin assignment, can be changed based on application requirement

The following chapter explains how to design.

**User Manual**

# NDA Confidential

# 2.1 DA16200 Power Supply

## 2.1.1 **Power Management**

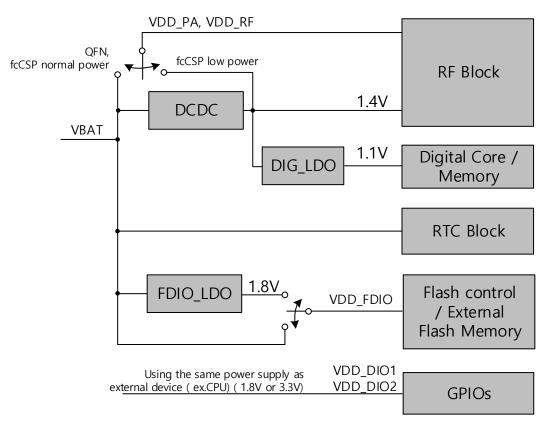

The DA16200 has one internal DC-DC converter and several LDOs to supply power to all internal sub-blocks. Power management does the on-off control of these regulators and is implemented through the register setting inside the RTC block.

### Figure 2: Power Management Block Diagram

Details of the internal DC-DC converters and LDOs are explained below:

- DC-DC converter: from the power supply of external VBAT input, it generates 1.4 V power for the digital LDO and RF block

- LDO for digital Blocks: from the DC-DC output, it generates 1.1 V power which is used for digital blocks

- LDO for I/O and external flash memory:

- This LDO output is used only for 1.8 V digital I/O applications

- From external VBAT power input, it generates 1.8 V output voltage which is used for digital I/O power domain in 1.8 V digital I/O applications

- It is also used for external flash memory

- For 3.3 V digital I/O applications, external power (3.3 V) is directly supplied for digital I/O power

- FDIO\_LDO\_OUT supports only 1.8 V

With the internal DC-DC converters and LDOs, all the power necessary for DA16200's internal subblocks are sufficiently generated.

| User Manual | Revision 1.3 | 14-Oct-2020 |

|-------------|--------------|-------------|

|-------------|--------------|-------------|

**NDA Confidential**

#### **Table 1 Power Pin Descriptions**

| QFN<br>#Pin | fcCSP<br>#Pin | Pin Name                    | Туре          | Description                                                                |

|-------------|---------------|-----------------------------|---------------|----------------------------------------------------------------------------|

| 1           |               | GND                         | GND           | Ground                                                                     |

| 2           | D12           | VDD_ANA                     | VDD           | RF VDD                                                                     |

| 13          | M8            | VDD_DIO2                    | VDD           | Supply power for digital I/O<br>GPIOC6~GPIOC8, TMS/TCLK, TXD/RXD           |

| 20          | M4            | VDD_FDIO                    | VDD           | Flash IO Power                                                             |

| 21          |               | FDIO_LDO_OUT                | AIO           | Flash and IO Ido output and connect to external<br>capacitor for flash LDO |

| 22          | L3            | VDD_DIG                     | VDD           | Digital power and connect to external cap. for DIG LDO                     |

| 24          | M2            | VBAT                        | VDD           | Supply power for internal DC-DC, DIO_LDO, and analog IP                    |

| 25          | L1            | DCDC_LX                     | AIO           | Internal DC-DC feedback input for digital block supply                     |

| 26          | J1            | DCDC_FB                     | AIO           | Internal DC-DC feedback output for digital block supply                    |

| 35          | C1            | VDD_DIO1                    | VDD           | Supply power for digital I/O<br>GPIOA0~GPIOA11                             |

| 45          | A7            | VDD_DA                      | VDD           | Tx DA power and RTC block power                                            |

| 46          | B8            | VDD_PA                      | VDD           | Supply power for integrated power amplifier                                |

| 47          |               | GND                         | GND           | Ground                                                                     |

|             |               | n: A1, A9, B6, B10, B12, C7 | 7, C9, C11, I | D8, D10, F6, F8, F10, F12, G5, G7, G9, H4, H8,                             |

H10, J3, K2, L5, M6, M12, E5

### 2.1.2 VBAT

DA16200 can operate one source for an I/O interface and internal power source (LDO and DC/DC converter) so it is important to reduce the noise component in this power line. All the input decoupling capacitors should be located nearby DA61200 and the thickness of power traces should be higher than 0.3 mm.

## 2.1.3 Internal DC/DC

DA16200 contains one DC/DC converter for the analog and digital part. This DC/DC converter needs to connect a series 4.7  $\mu$ H power inductor for high-power efficiency and a shunt 10  $\mu$ F capacitor to reduce switching noise, so the inductor and capacitor are located as close as possible for stable power supply. And 1  $\mu$ F is required to other bypass capacitors for power supply.

## 2.2 RF

The RF application circuit is important to get an optimum performance from the device. An improper circuit and layout can cause performance degradation for sensitivity, output power, error vector magnitude (EVM) and spectral mask.

## 2.2.1 Antenna

The antenna is the element used to convert the guided waves on the PCB traces to free-space electromagnetic radiation. The position and layout of the antenna is very important to increase coverage and data rates. Section 2.2.2 has details about a tested antenna part.

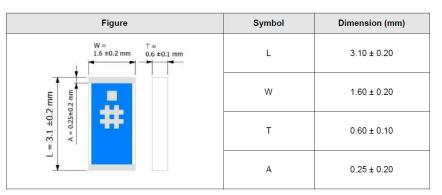

## 2.2.2 Antenna information of DA16200 EVK

- Part number

WALSIN RFECA32160AM1T62

- Dimension

Figure 3: Tested Antenna Dimension

• Tested Antenna usage example

| User Manual | Revision 1.3 | 14-Oct-2020 |

|-------------|--------------|-------------|

|             |              |             |

**NDA Confidential**

Radiation Pattern

Figure 5: Tested Antenna Radiation Pattern

Below is the consideration for the antenna part.

- 1. Put the antenna on the edge or corner of the PCB.

- 2. Signal lines must not be routed across the antenna elements on all the layers of the PCB.

- 3. The ground is needed for copper keep-out on all layers include inner layers.

- 4. Matching components for the antenna are needed to optimize each board.

- 5. The return loss measured at the matching components of the antenna need to be better than -10 dB to get the optimum system performance.

|      | Manual |  |

|------|--------|--|

| User | Manual |  |

## 2.2.3 RF Input Requirement

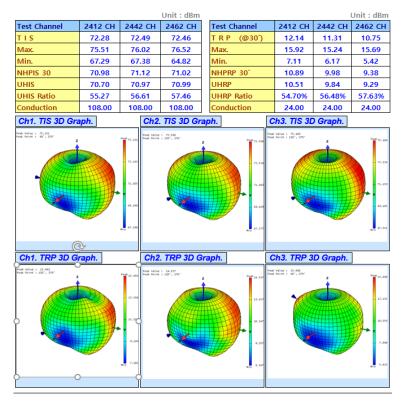

The RF part must have matching components and an RF filter to suppress any harmonic element. A Passive filter which is made by a lumped component can meet the system requirements because the DA16200 has good harmonic suppression performance.

#### Table 2 Recommended LC filter

The RF line needs to be isolated by using ground plane with clearance to ensure good performance (output power, EVM, SEM and sensitivity).

## 2.3 Clock

### 2.3.1 Main Clock

DA16200 has a crystal oscillator for the main clock source, which supports the external crystal clock. Basically, the external clock is 40 MHz. Make sure that the load capacitance is tuned based on the board parasitic so that the frequency tolerance is within ±20 ppm. And the clock line needs to route closer to the XTAL routing to avoid any phase noise degradation.

## 2.3.2 RTC Clock

The 32.768 kHz RTC clock source is necessary for the free-running counter in the RTC block. The external clock is 32.768 kHz. Make sure that the load capacitance is tuned based on the board parasitic so that the frequency tolerance is within  $\pm 250$  ppm.

**User Manual**

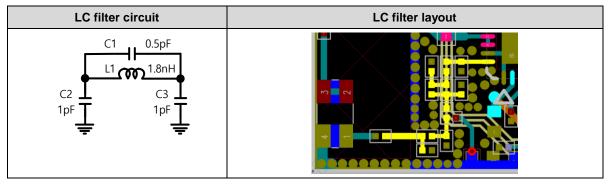

## 2.4 Serial Flash

#### 2.4.1 Serial Flash Interface

The QSPI master supports 4-line SPI communication with commercial flash memory devices and uses a Motorola SPI-compatible interface among SPI communication modes. The highest communication speed is the same as the AMBA bus clock, and the speed is adjustable in integer multiples. The designed QSPI supports 4-/2-/1-line types depending on the purpose. These types should be combined. Especially when 1-line communication mode is used, it can be used as the SPI master.

## 2.4.2 Serial Flash Selection Guide

• The '.img' of DA16200 has a structure as shown in Figure 7.

| Image <sup>•</sup> header |

|---------------------------|

| Multi image info (12B) .  |

| SFDP                      |

| RTOS · image              |

#### Figure 7: DA16200 Image Structure

- SFDP (Serial Flash Discoverable Parameters) is a standard table for the main parameters of serial flash defined by JEDEC. This is information about the characteristics access timing, supported commands, and delay parameter of each serial flash manufactured by various vendors, and those should be optimized for each serial flash.

- Currently the DA16200 SDK supports SFDP tables for 7 types of serial flashes listed in Table 3.

#### **Table 3 Recommended Serial Flash List**

| Vendor   | Part number             |

|----------|-------------------------|

| ISSI     | IS25LQ032B              |

| ISSI     | IS25WP016D              |

| ISSI     | IS25LP032D (IS25LP016D) |

| Winbond  | W25Q032JVSNIQ           |

| Winbond  | W25Q16JVSNIQ            |

| Macronix | MX25L3233F              |

| Macronix | MX25U3232F              |

• If customers want to use other types of serial flash, then the extraction (from serial flash specification) and optimization of the SFDP parameters is needed. And a new serial flash should be used, the schedule shown in Table 4 is required, which the customer should take into consideration in their project planning.

#### **Table 4 New Flash verification process**

| New Flash verification process                            |  |  |  |  |

|-----------------------------------------------------------|--|--|--|--|

| 'D': date of receiving the board-adopted new serial flash |  |  |  |  |

|                                                           |  |  |  |  |

| a. Extract SFDP parameter                                 |  |  |  |  |

| - D + 10                                                  |  |  |  |  |

| b. Apply SFDP table to img & function test                |  |  |  |  |

| - D + 15                                                  |  |  |  |  |

| - Function test in normal condition                       |  |  |  |  |

| c. Reliability test                                       |  |  |  |  |

| - Function test in severe condition                       |  |  |  |  |

| - D + 21                                                  |  |  |  |  |

| d. Final SDK release                                      |  |  |  |  |

| - D + 30                                                  |  |  |  |  |

|                                                           |  |  |  |  |

#### **User Manual**

Revision 1.3

#### 14-Oct-2020

# **3 PCB Layout Example**

## 3.1 Grounding

- Make the internal ground area as solid as possible. Do not break the ground into pieces.

- Provide good solid ground by using multiple vias

- Fill as much ground as possible in the area between the walls of shield cavities and the outline of the RF section

- Connect each ground pin or via to the ground plane individually.

- Put the Ground via on the PAD of the QFN package

Figure 8: Ground vias on PAD

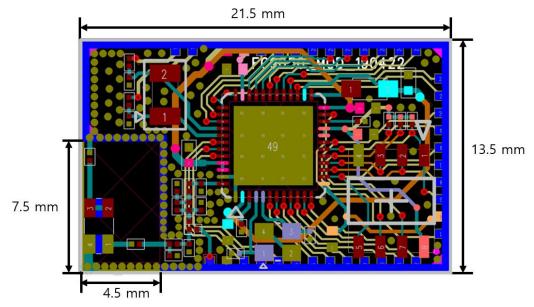

# 3.2 PCB Layout Example

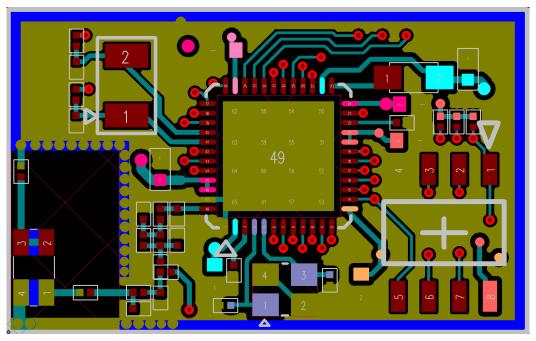

• Layer 1 (Top)

Figure 9: PCB Layout Example: Top layer

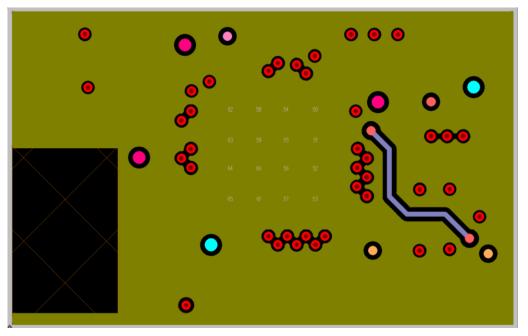

• Layer 2

Figure 10: PCB Layout Example: 2nd layer

# **UM-WI-006**

# DA16200 H/W Design Guide

**NDA Confidential**

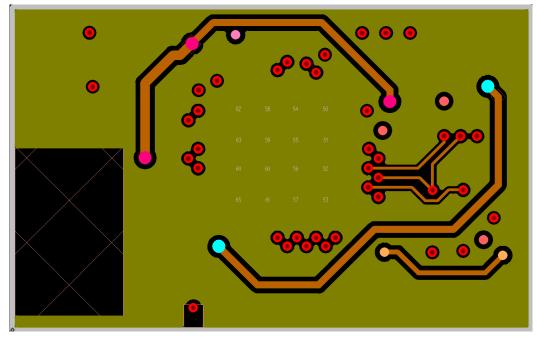

• Layer 3

Figure 11: PCB Layout Example: 3rd layer

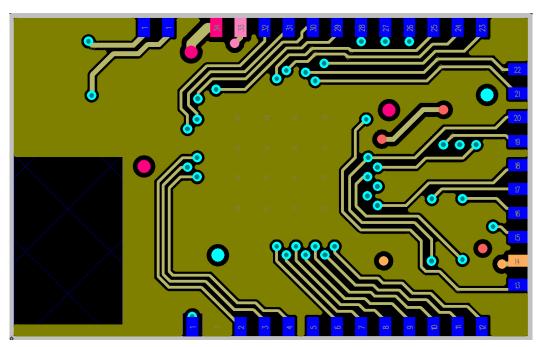

• Layer 4(Bottom)

Figure 12: PCB Layout Example: Bottom layer

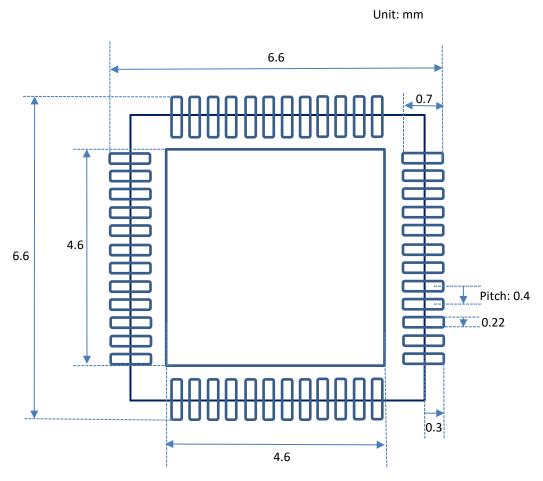

# 4 Recommended Footprint

Figure 13: DA16200 Ground Footprint

# **Revision History**

| Revision | Date        | Description                                 |

|----------|-------------|---------------------------------------------|

| 1.0      | 14-Oct-2020 | Table 3 Updated,                            |

| 1.3      |             | Section 2.1.1 Power Management Updated      |

| 1.2      | 29-Oct-2019 | Removed Draft status; finalized for release |

| 1.1      | 21-Oct-2019 | Editorial review                            |

| 1.0      | 30-Aug-2019 | Preliminary DRAFT Release                   |

**User Manual**

#### **NDA Confidential**

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### Disclaimer

Unless otherwise agreed in writing, the Dialog Semiconductor products (and any associated software) referred to in this document are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of a Dialog Semiconductor product (or associated software) can reasonably be expected to result in personal injury, death or severe property or environmental damage. Dialog Semiconductor and its suppliers accept no liability for inclusion and/or use of Dialog Semiconductor products (and any associated software) in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, express or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications. Notwithstanding the foregoing, for any automotive grade version of the device, Dialog Semiconductor reserves the right to change the information published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications, in accordance with its standard automotive change notification process.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document is subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog, Dialog Semiconductor and the Dialog logo are trademarks of Dialog Semiconductor PIc or its subsidiaries. All other product or service names and marks are the property of their respective owners.

© 2020 Dialog Semiconductor. All rights reserved.

# **Contacting Dialog Semiconductor**

United Kingdom (Headquarters) Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

#### Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

#### The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822 Email:

enquiry@diasemi.com

#### **User Manual**

CFR0012

#### North America

*Dialog Semiconductor Inc.* Phone: +1 408 845 8500

#### Japan

Dialog Semiconductor K. K. Phone: +81 3 5769 5100

#### Taiwan

*Dialog Semiconductor Taiwan* Phone: +886 281 786 222

Web site: www.dialog-semiconductor.com

#### Hong Kong

Korea

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

#### Phone: +86 755 2 China (Shanghai)

Dialog Semiconductor Korea Phone: +82 2 3469 8200 China (Shenzhen) Dialog Semiconductor China Phone: +86 755 2981 3669

Dialog Semiconductor China Phone: +86 21 5424 9058

#### Revision 1.3

# 14-Oct-2020