# Errata SLG47105 CE-GP-003

## Abstract

This document contains the known errata for SLG47105 and the recommended workarounds.

## 1 Information

Package(s) 20-pin STQFN: 2 mm x 3 mm x 0.55 mm, 0.4 mm pitch

## 2 Errata Summary

#### Table 1: Errata Summary

| Issue # | Issue Title                                                                               |

|---------|-------------------------------------------------------------------------------------------|

| 1       | Dependence of Current Consumption on I2C Read/Write Operation                             |

| 2       | Shifted Rising Edge of the Cycle when the Fast Decay is Applied                           |

| 3       | Incorrect 32 mV and 64 mV Hysteresis Operation with ACMPxH                                |

| 4       | ACMPxH erroneous behavior when used with Wake-Sleep controller for certain Vref selection |

## 3 Errata Details

#### 3.1 Dependence of Current Consumption on I<sup>2</sup>C Read/Write Operation

#### 3.1.1 Effect

Chip Current Consumption

#### 3.1.2 Conditions

When I<sup>2</sup>C Read/Write operation stops at certain addresses.

#### 3.1.3 Technical Description

Read/Write operation at certain addresses via  $I^2C$  can cause significant current consumption increase. The amount of current drawn by the chip is highly dependent on  $V_{DD}$  voltage that is applied to the IC, please see Table 2.

| V <sub>DD</sub> | Current Consumption After I <sup>2</sup> C<br>Interaction with Problematic Addresses | Normal Current Consumption After I <sup>2</sup> C<br>Interaction |

|-----------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 2.3 V           | 39-150 μA                                                                            | 0.033 μA                                                         |

| 2.5 V           | 45-93 μA                                                                             | 0.033 μA                                                         |

| 3.3 V           | 84-339 μA                                                                            | 0.035 μA                                                         |

| 4.0 V           | 121-488 μA                                                                           | 0.035 μA                                                         |

| 5.0 V           | 177-710 μA                                                                           | 0.040 μA                                                         |

| 5.5 V           | 206-822 μA                                                                           | 0.040 μA                                                         |

#### **Table 2: Chip Current Consumption**

I<sup>2</sup>C Address pointer increases after the stop of I<sup>2</sup>C operation. So, in case when Read/Write command stops right before the problematic address, the current consumption increase will appear.

Value of an excess current changes relative to the value of a register being read/written. Most likely, current consumption will increase in the case of reading «1» from the problematic register or writing «0» to it.

Errata

**Revision 1.2**

#### 3.1.4 Workaround

The best workaround is not to stop the I<sup>2</sup>C Read/Write operation on the problematic addresses (for example, instead of reading just 0x4E and 0x4F addresses, the Sequential Read Command should include addresses 0x4E, 0x4F, 0x50). This helps to keep an increase time as short as possible.

Also, the problem could be solved by initiating another Read/Write operation with an unaffected address. For the known problematic addresses refer to Table 3.

| Address   | 0x48 | 0x49 | 0x4A | 0x4B | 0x4D | 0x4E | 0x4F | 0x89 |

|-----------|------|------|------|------|------|------|------|------|

| Operation | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | W    | W    |

|           |      |      |      |      |      |      |      |      |

| Address   | 0x8A | 0x8B | 0xA4 | 0xA5 | 0xF9 | 0xFB | 0xFC |      |

| Operation | R    | W    | R/W  | R/W  | W    | R/W  | W    |      |

#### Table 3: Known Problematic Addresses

#### 3.2 Shifted Rising Edge of the Cycle when the Fast Decay is Applied

#### 3.2.1 Effect

High Side Pin

#### 3.2.2 Conditions

When Fast Decay mode is applied.

#### 3.2.3 Technical Description:

In the Fast Decay mode, the negative voltage, created by the inductive load on the HV\_GPO\_HD pin, discharges the internal Charge Pump due to the parasitic p-n junction. Because of this, the Rising Edge on the High Side pin shifts. The duration of the shift depends on the Duty Cycle, the High Side input voltage (V<sub>DD2</sub>), and the PWM frequency.

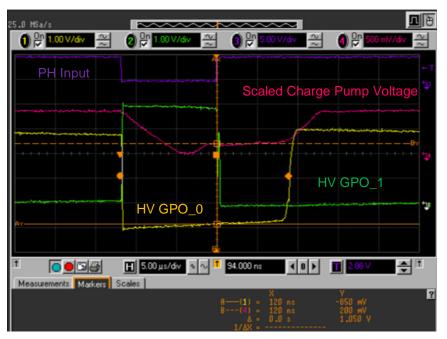

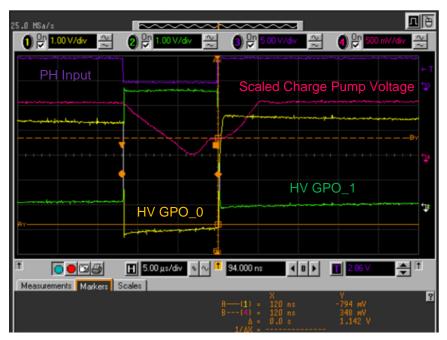

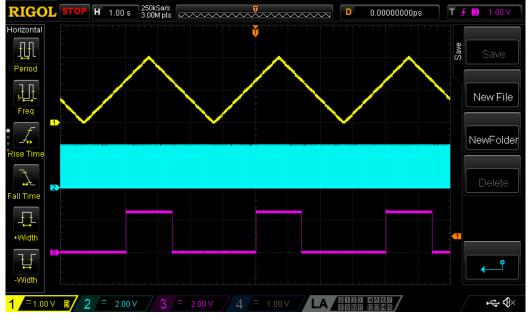

For example, the PWM Duty Cycle values higher than 75 % in a combination with  $V_{DD2}$  voltage lower than 3.75 V, and the Fast Decay settings applied can cause this problem, please see Figure 1 and Figure 2.

**Note:** HV GPO\_0/1 are set to H-Bridge, Slow Slew Rate, Mode Control: PH-EN. In this case, EN is «HIGH», DECAY MODE Input is «LOW» (Fast Decay).

Figure 1: Shifted Rising Edge (V<sub>DD2</sub> = 3.0 V, Fast Decay, PWM = 75+ %)

Figure 2: Discharge of the Internal Charge Pump ( $V_{DD2}$  = 3.75 V, Fast Decay, PWM = 75+ %)

#### 3.2.4 Workaround:

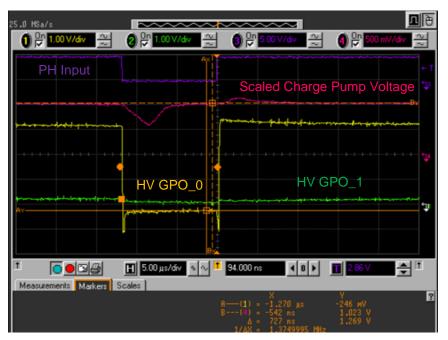

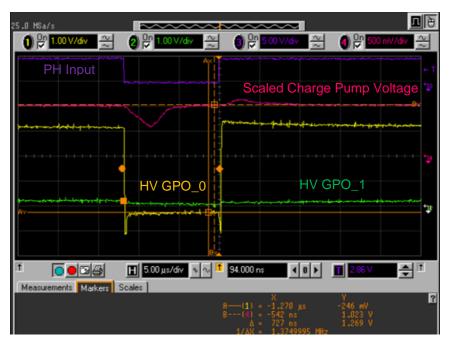

The best way to exclude a possibility of such a malfunction is to use the Slow Decay option for the H-Bridge instead of the Fast Decay. No evidence of improper behavior has been discovered when  $V_{DD2}$  is higher than 3.75 V and the Fast Decay settings are applied. The chip is not affected by this problem when the load is resistive, because the negative voltage will appear on a pin only when the inductive load discharges.

| Errata | Revision 1.2 |

|--------|--------------|

|        |              |

#### SLG47105 Errata

Figure 3: Rising Edge is Not Shifted (V<sub>DD2</sub> = 3.75 V, Slow Decay, PWM = 75+ %)

Figure 4: Low V<sub>DD2</sub> Voltage Operation (V<sub>DD2</sub> = 2.75 V, Slow Decay, PWM = 75+ %)

#### 3.3 Incorrect 32 mV and 64 mV Hysteresis Operation with ACMPxH

#### 3.3.1 Effect

ACMP0H and ACMP1H

#### 3.3.2 Conditions

$V_{\text{DD}}$  > 4.6 V, with hysteresis 32 mV at Vref range 1.344 V to 2.016 V.

$V_{DD}$  > 3.6 V, with hysteresis 32 mV at Vref range 1.344 V to 1.504 V.

| En |   | a |  |

|----|---|---|--|

|    | a | a |  |

#### SLG47105 Errata

$V_{DD}$  > 4.6 V, with hysteresis 64 mV at Vref range 1.376 V to 1.664 V.

3.6 V < V<sub>DD</sub> < 4.6 V, with hysteresis 64 mV only when Vref is set to 1.376 V.

#### 3.3.3 Technical Description

If using ACMPxH in with 32 mV or 64 mV hysteresis, ACMPxH output could be glitching when ACMPxH positive input (IN+) is close to the negative input (IN-). It can happen when  $V_{DD}$  higher 4.6 V and Vref is in a range from 1.344 V to 2.016 V for 32 mV hysteresis, and Vref is in a range from 1.376 V to 1.664 V for 64 mV hysteresis.

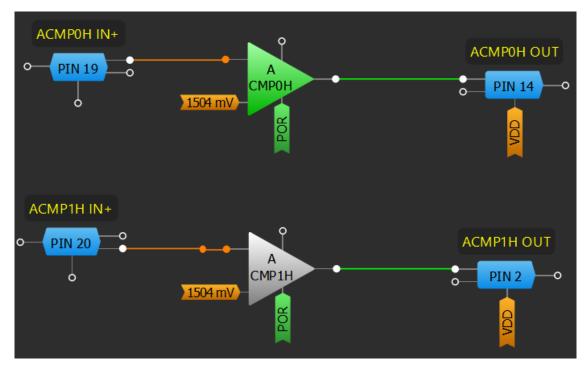

#### Figure 5: Testing Design

Channel 1 (yellow/top line) - PIN#19 (ACMP0H IN+) Channel 2 (light blue/2nd line) - PIN#14 (ACMP0H OUT)

#### SLG47105 Errata

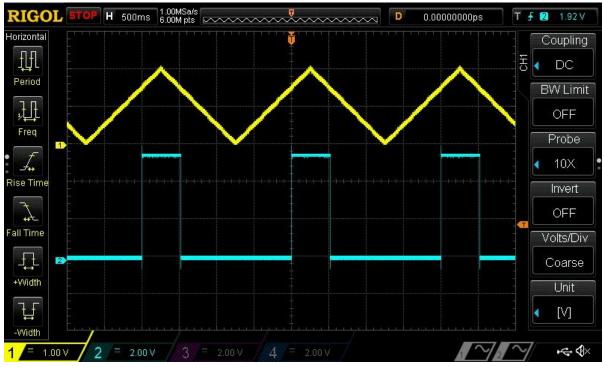

#### 1. Waveform at Vref = 1504 mV, hysteresis is equal to 32 mV.

#### Figure 6: ACMP Output during Glitching

2. Waveform at Vref = 1504 mV, hysteresis is equal to 32 mV (zoomed rising edge).

Figure 7: Zoomed ACMP Output during Glitching

| r r | - | ta |  |

|-----|---|----|--|

|     | a | ια |  |

#### SLG47105 Errata

#### 3.3.4 Workaround

Use the deglitch filter connected to the ACMPxH output.

Avoid conditions described in paragraph 3.3.2.

Decrease the reference to avoid conditions described in paragraph 3.3.2 at IN- and add the IN+ gain to keep the needed threshold.

## 3.4 ACMPxH erroneous behavior when used with Wake-Sleep controller for certain Vref selection

#### 3.4.1 Effect

ACMP0H and ACMP1H

#### 3.4.2 Conditions

ACMPxH is used with the macrocell CNT0 configured as a wake-sleep controller (WS Ctrl).

WS Ctrl Short wake time mode is selected, for Vref range 1.312 V to 1.440 V.

WS Ctrl Normal wake time is selected, for two Vref ranges 0.832 V to 0.896 V and 1.312 V to 1.440 V.

#### 3.4.3 Technical Description

When WS Ctrl is used for controlling the power on/off of analog macrocells ACMPs for power saving, ACMPxH shows erroneous behavior for certain Vref selection. Vref transient settling error is observed for both WS Ctrl Wake time modes, Short wake time and Normal wake time (selections under CNT0 settings).

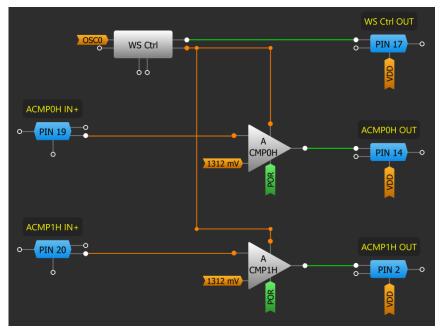

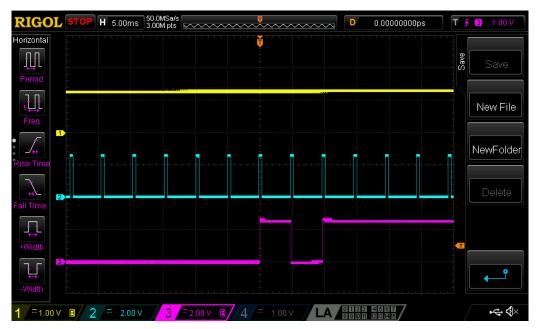

#### Figure 8: Testing Design

Channel 1 (yellow/top line) - PIN#19 (ACMP0H IN+)

Channel 2 (light blue/2nd line) - PIN#17 (WS Ctrl OUT)

Channel 3 (magenta /3rd line) - PIN#14 (ACMP0H OUT)

| Errata | Revision 1.2 |

|--------|--------------|

|        |              |

### SLG47105 Errata

1. Waveform at Vref = 1312 mV, hysteresis is equal to 32 mV

Figure 9: ACMP0H Output during Glitching

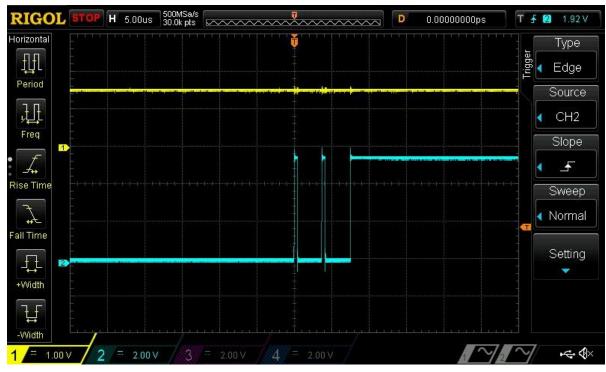

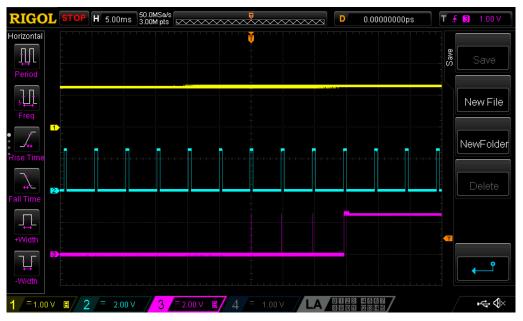

2. Waveform at Short wake time mode, Vref = 1312 mV, hysteresis is equal to 32 mV (zoomed rising edge).

Figure 10: Zoomed ACMP Output during Glitching at Short wake time mode

3. Waveform at Normal wake time mode, Vref = 1312 mV, hysteresis is equal to 32 mV (zoomed rising edge).

Figure 11: Zoomed ACMP Output during Glitching at Normal wake time mode

#### 3.4.4 Workaround

1. If ACMP is used with WS Ctrl counter, CNT0, avoid conditions described in paragraph 3.4.2.

2. Decrease the reference to avoid conditions described in paragraph 3.4.2 at IN- and add the IN+ gain to keep the needed threshold.

## **Document Revision History**

| Revision | Date        | Description                              |

|----------|-------------|------------------------------------------|

| 1.2      | 27-Jul-2021 | Added issues #3 and #4                   |

| 1.1      | 24-Jun-2020 | Updated according to new Dialog's format |

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **Disclaimer**

Unless otherwise agreed in writing, the Dialog Semiconductor products (and any associated software) referred to in this document are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of a Dialog Semiconductor product (or associated software) can reasonably be expected to result in personal injury, death or severe property or environmental damage. Dialog Semiconductor and its suppliers accept no liability for inclusion and/or use of Dialog Semiconductor product (or applications and therefore such inclusion and/or use is at the customer's own risk.

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, express or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications. Notwithstanding the foregoing, for any automotive grade version of the device, Dialog Semiconductor reserves the right to change the information published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications published in this document, including, without limitation, the specification and the design of the related semiconductor products, software and applications, in accordance with its standard automotive change notification process.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document is subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog, Dialog Semiconductor and the Dialog logo are trademarks of Dialog Semiconductor Plc or its subsidiaries. All other product or service names and marks are the property of their respective owners.

© 2021 Dialog Semiconductor. All rights reserved.

## **Contacting Dialog Semiconductor**

United Kingdom (Headquarters) Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

#### Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

#### The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822 Email: enquiry@diasemi.com

#### North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

#### Japan

Dialog Semiconductor K. K. Phone: +81 3 5769 5100 Taiwan

#### Dialog Semiconductor Taiwan

Phone: +886 281 786 222 Web site: www.dialog-semiconductor.com

#### Hong Kong

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

#### Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8200

#### China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

#### China (Shanghai) Dialog Semiconductor China Phone: +86 21 5424 9058

Errata

Revision 1.2