**Company confidential**

# **Application note**

## DA14580 Checklist for schematic and PCB layout

## AN-B-018

Abstract

This document is a guideline and checklist for DA14580 schematics and PCB layouts.

-

DA14580 Checklist for schematic and PCB layout

**Company confidential**

### Contents

| Со | ntents |            |                                                  | 2 |

|----|--------|------------|--------------------------------------------------|---|

| 1  | Term   | s and defi | nitions                                          | 3 |

| 2  | Refer  | ences      |                                                  | 3 |

| 3  | Check  | king the s | chematic and the PCB layout                      | 4 |

|    | 3.1    | GPIO por   | rts                                              | 4 |

|    | 3.2    | 16 MHz (   | crystal oscillator                               | 4 |

|    | 3.3    | 32 kHz ci  | rystal oscillator                                | 4 |

|    | 3.4    | VDCDC a    | nd VDCDC_RF filtering and decoupling             | 5 |

|    | 3.5    | Buck- or   | Boost-mode                                       | 5 |

|    | 3.6    | Debuggir   | ng interface                                     | 5 |

|    | 3.7    | RF input   | and output matching                              | 5 |

|    |        | 3.7.1      | DA14580 Antenna matching circuit                 | 6 |

|    |        | 3.7.2      | Antenna placement                                | 6 |

|    |        | 3.7.3      | Printed antenna example                          | 6 |

| 4  | PCB la | ayout exa  | mples                                            | 7 |

|    | 4.1    | WLCSP p    | ackage: PCB design examples for 16 MHz crystal   | 7 |

|    |        | 4.1.1      | DA14580 WLCSP ball pattern                       | 8 |

|    |        | 4.1.2      | Single-layer PCB                                 | 9 |

|    |        | 4.1.3      | Multi-layer PCB with regular vias                | 9 |

|    |        | 4.1.4      | Multi-layer PCB with micro vias1                 | 0 |

|    | 4.2    | Single-la  | yer PCB with access to a ball on an inner ring:1 | 0 |

| 5  | Revis  | ion histor | y1                                               | 1 |

**Company confidential**

#### **1** Terms and definitions

- ADC Analog to Digital Converter

- BLE Bluetooth Low Energy

- GPIO General Purpose Input Output

- PCB Printed Circuit Board

- SPI Serial Peripheral Interface

- UART Universal Asynchronous Receiver/Transmitter

#### 2 References

- 1. DA14580 Datasheet, Dialog Semiconductor

- 2. AN-B-001: DA14580 Booting from Serial Interfaces, Application note, Dialog Semiconductor

- 3. AN-B-009: DA14580 Crystal oscillator PCB layout guidelines, Application note, Dialog Semiconductor

| An | nling | tion | noto |

|----|-------|------|------|

| AP | μπεα  |      | note |

#### 3 Checking the schematic and the PCB layout

#### 3.1 GPIO ports

- For UART communication, check that preferably the UART ports P0\_4 and P0\_5 are used. These are the default ports for the DA14580\_01, and these are part of the Boot-Sequence. If not possible, use either one of the other UART pairs: i.e. P0\_0/P0\_1 or P0\_2/P0\_3.

- When not using the ADC, make sure the voltage levels at the ports P0\_0 thru P0\_3 are not higher than Vbat3V in order to prevent that these signals are interfering with internal ADC measurements.

- In case the ADC is being used, check that the voltages at the ADC input ports, P0\_0 thru P0\_3, are not higher than Vbat3V + 0.2V and never exceeding the maximum level of 3.45 V.

- When an external SPI slave device is used for booting, make sure following ports are being used: P0\_0, P0\_3, P0\_5 and P0\_6 for resp. SCK, CS, MISO and MOSI.

For details, see *"Table 4: Development Mode Peripheral Pin Mapping"* in the datasheet.

- Refer also to Application Note AN-B-001.pdf.

#### 3.2 16 MHz crystal oscillator

- Select a crystal having a max. ESR lower than 100 Ohm. Higher ESR values will increase the 16 MHz crystal oscillator start-up time. For crystals having 50 to 80 Ohm ESR values, start-up time is about 2 to 2.5 msec, for crystals having ESR of 100 Ohm or higher, it can be as long as 4 or 5 msec. Take this into account. Smaller sized 16 MHz crystal packages (e.g. size 2016) tend to have higher ESR values than larger cans (e.g. size 3225) have.

- No additional load capacitors required, also no capacitor pads foreseen on the PCB. The required crystal load capacitors are provided internally. The stray capacitance to the 16 MHz crystal really must be minimised to avoid cross-talk to the 16 MHz oscillator.

- Keep the connections to the 16 MHz crystal as short as possible to minimize picking up interference or noise.

- Keep UART lines, debug lines and other clock lines away from the 16 MHz crystal oscillator. This yields also for traces at the underlying layer, which may be a ground plane. The oscillator is very sensitive and is easily disturbed which may lead to un-stable BLE operation when e.g. clock signals are running by closely.

- Most sensitive ports for the 16MHz crystal oscillator are P1\_2 and P1\_3; these ports will generate much cross-talk to the 16 MHz oscillator when toggled fast. Make sure these ports are not toggling when the 16 MHz oscillator is active. It is safe to use them for static purposes, though.

- Refer also to Application Note AN-B-009.pdf.

#### 3.3 32 kHz crystal oscillator

- If the used 32KHz crystal has required load capacitance in the range of 6 7 pF, no additional load capacitors are required. Please, also do not place capacitor pads on the PCB. Only if the required load capacitance is higher than 7 pF, add additional capacitance to the Xtal32K pins. Please note that the maximum allowed load capacitance is 9 pF.

- Although less critical than the 16 MHz crystal oscillator, keep its connections short.

- Port P2\_2 of the QFN40 package and port P3\_3 of the QFN48 package potentially can disturb the 32KHz crystal oscillator. Don't let traces connected to these ports run close or parallel to the Xtal32Kp side of the Xtal32K oscillator.

| App       | licatio | on note |

|-----------|---------|---------|

| · · · · · |         |         |

#### 3.4 VDCDC and VDCDC\_RF filtering and decoupling

- Good filtering and decoupling of the VDCDC output from the VDCDC\_RF supply pin is important for a good RF performance. The 1uF decoupling capacitors should be placed as close as possible to the supply pins.

This is of special importance in a boost mode system, where VBAT1V might be close to VDCDC. In this case the noise at VDCDC is high and RF performance is affected. In this case a higher decoupling capacitor (e.g. 2uF) might be needed.

In rare cases, where VBAT1V will be close to VBAT3V, placing a 1uF capacitor at VBAT3V and VBAT RF is recommended.

- **Inductor:** choose a type with a high resonance frequency, preferably higher than 75 MHz. This results in a lower stray capacitance and minimises the HF noise at VDCDC\_RF. Its maximum rated current should be at least 80mA for a buck-mode application, preferably 100mA or higher. When the inductor is in saturation, it cannot operate well anymore, resulting in high HF-noise and HF-ripple and worse BLE performance. An inductor value of 2.2 µH is recommended.

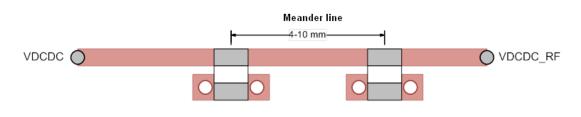

- Capacitors: use a 1 µF value for both filtering caps at VDCDC and VDCDC\_RF, preferably low inductance types or 0201 (0603M) sized ceramic multilayer capacitors, e.g. 1µF, 6.3V, X5R types. For grounding, try to minimize the mounted inductance. Provide either "via in pad" if possible, or if not possible, use double vias as in below picture.

- Use a meander-shaped trace with a length of about 7 mm between the VDCDC pin and the VDCDC\_RF pin. This inductance reduces the HF-noise and HF-ripple at the VDCDC\_RF pin.

VDCDC\_RF filtering and decoupling

#### 3.5 Buck- or Boost-mode

• Check the schematic for correct Buck- or Boost-Mode configuration.

#### 3.6 Debugging interface

Check for availability of following signals on e.g. test-points, pins or a header in order to have easy access to them for programming and for debugging: JTAG SW\_CLK and SWDIO, UART RX, UART TX, VPP, Vbat3V, GND, Reset.

#### 3.7 RF input and output matching

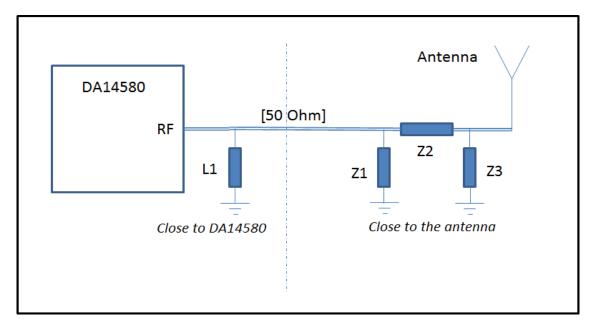

- For optimal matching of the DA14580 to 50 Ohm, make sure to place a shunt inductor as close as possible to the RFIO pin. The value of this shunt inductor depends on the package.

WL-CSP package: 3.3nH inductor; both QFN packages: 3.9nH inductor. This shunt inductor is L1 in below figure in section 3.7.1. This matching ensures best RF sensitivity and highest RF output power.

- Further, foresee some matching components for antenna matching; these parts should be close to the antenna. Most universal is a PI matching network, having two shunt components and one series component: Z1, Z3 and Z2. Type and value fully depend on the antenna type, but typically

**Application note**

25-Apr-2018

small pF caps and low nH inductor values are expected here.Maybe not all three parts are required to have a good matching. The connecting PCB trace should have a characteristic impedance of 50 Ohm. See picture in section 3.7.1.

The free Agilent tool 'AppCad' can calculate the characteristic trace impedances when substrate and trace dimensions are known. Also online RF calculators are available.

#### 3.7.1 DA14580 Antenna matching circuit

#### 3.7.2 Antenna placement

Whether a PCB printed antenna is being used, or e.g. a ceramic chip antenna, make sure no copper is under the antenna, and no traces are running under the antenna area. The antenna must be able to radiate freely. The ceramic chip antenna mostly requires some copper-free area around it; refer to the antenna manufacturer's antenna layout guide.

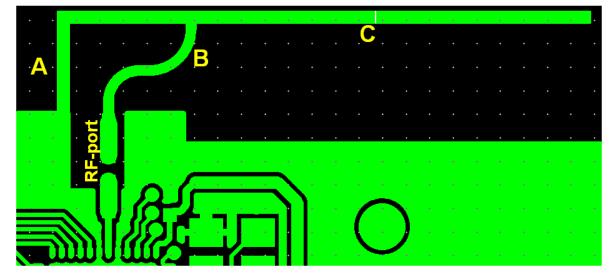

#### 3.7.3 Printed antenna example

Below the printed PCB antenna used in the Dialog's Keyboard Reference Design is shown. The design is a so-called inverted F-antenna. One can copy and paste this design on any PCB material. Gerber files and design files can be provided.

| ۸n | nlicat | ion n | oto |

|----|--------|-------|-----|

| AP | plicat |       | ole |

#### **Company confidential**

#### PCB Antenna in Keyboard Reference Design

Measures of the shown printed antenna:

- A 4 mm long, 0.53 mm wide this is for the vertical part only

- B 5 mm long, 0.40 mm wide the antenna feed trace

- C 23 mm long in total, 0.53 mm wide the section between A B is 5.5 mm long

The grid size in above picture is 1 mm

A PI-network for antenna matching components is provided too. Please make sure this matching circuit is present in your design. The antenna free space area should be 25 mm x 6 mm. Under and in this area there should be no ground planes, no traces and no components.

A very similar printed antenna is being used on Dialog's new (2014) evaluation kits.

#### 4 PCB layout examples

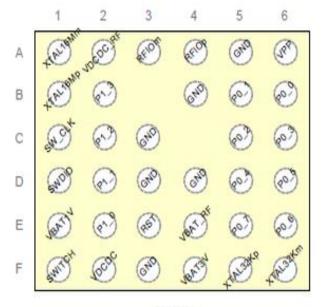

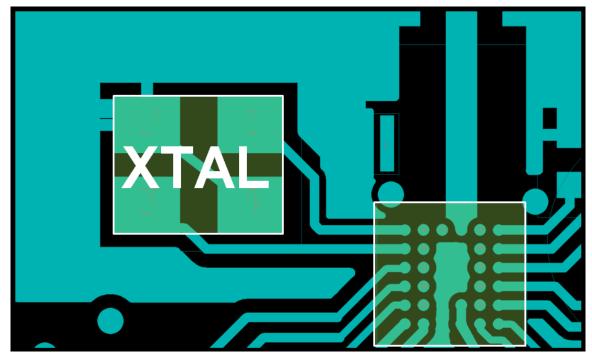

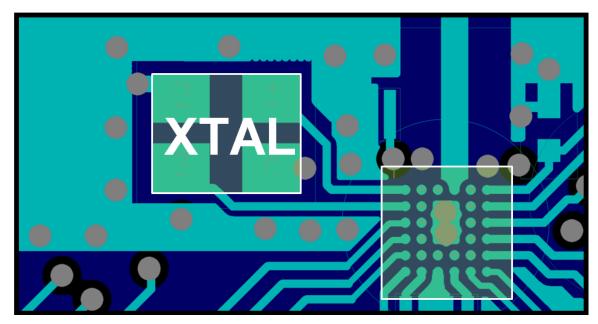

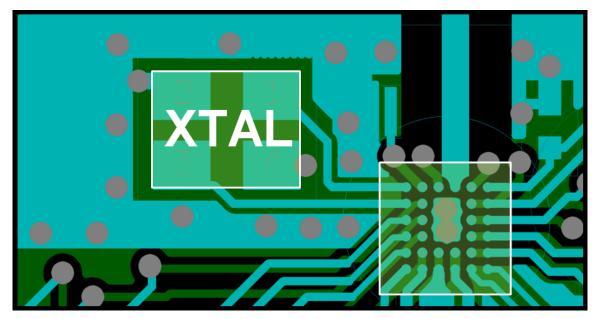

#### 4.1 WLCSP package: PCB design examples for 16 MHz crystal

The following paragraphs show some design examples for the DA14580 WLCSP package with different PCB structures. For the WLCSP package the inner ring connections (P1\_0, P1\_1, P1\_2, P1\_3, P0\_1, P0\_2, P0\_4 and P0\_7) can only be used with a Multi-layer PCB with micro vias. When micro vias are used it is recommended to place the micro vias in the middle of the balls/connections of the device.

| -  |          |       |      |

|----|----------|-------|------|

| Ap | plicati  | on no | to - |

| AD | טוונמנוי |       | ιe   |

|    |          |       |      |

-

#### DA14580 Checklist for schematic and PCB layout

#### **Company confidential**

## 4.1.1 DA14580 WLCSP ball pattern

Top View

| _     |     |      |     |      |

|-------|-----|------|-----|------|

| An    | nli | cati | ion | note |

| · • P |     |      |     |      |

**Company confidential**

#### 4.1.2 Single-layer PCB

The crystal is surrounded by a guard ring. This guard ring is connected to ground. Both crystal case ground connections are connected to ground. The inner ring of the DA14580 is not used since there is not enough space to route to these pins.

#### 4.1.3 Multi-layer PCB with regular vias

The oscillator circuit is shielded by a ground plane. The crystal is surrounded by a guard ring. This guard ring is connected to the ground plane using vias. Both crystal case ground connections are connected to ground. There should be no wires between the oscillator circuit and the ground plane. The inner ring of the DA14580 is not used since there is not enough space to route to these pins when using regular vias.

| Application note |  |

|------------------|--|

|                  |  |

**Revision 1.2**

#### **Company confidential**

#### 4.1.4 Multi-layer PCB with micro vias

The oscillator circuit is shielded by a ground plane. The crystal is surrounded by a guard ring. This guard ring is connected to the ground plane using vias. Both crystal case ground connections are connected to ground. There should be no wires between the oscillator circuit and the ground plane. The micro vias used to connect the inner pins of the DA14580 are located directly under the pads. This makes it possible to route the GPIO lines and e.g. the JTAG lines directly away from the oscillator circuit.

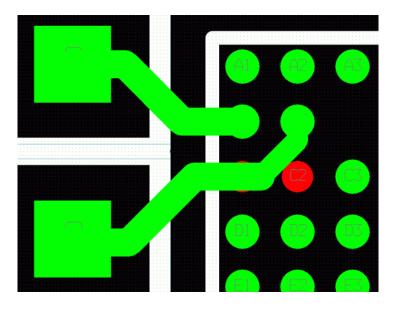

#### 4.2 Single-layer PCB with access to a ball on an inner ring:

An illustration example for having access to ball B2: two pins have to be sacrificed for this, in above example these are pins C1 and C2. This could be used for access to e.g. P0\_4 for having UART communication at P0\_4/P0\_5, either ports P0\_2/P0\_3 or P0\_6/P0\_7 have to be sacrificed.

| ote |

|-----|

|     |

DA14580 Checklist for schematic and PCB layout

## 5 Revision history

| Revision | Date         | Description                                                                                                  |

|----------|--------------|--------------------------------------------------------------------------------------------------------------|

| 0.1      | 18-Febr-2014 | Initial version.                                                                                             |

| 0.2      | 20-May-2014  | Updated for VDCDC decoupling. Template updated to latest version.<br>Back page: contact information updated. |

| 1.0      | 20-May-2014  | Final reviewed version.                                                                                      |

| 1.1      | 22-Aug-2014  | Updated sections 3.3 and 3.6                                                                                 |

| 1.2      | 25-Apr-2018  | Updated section 3.4.                                                                                         |

|  | App | licati | on | note |

|--|-----|--------|----|------|

|--|-----|--------|----|------|

#### **Company confidential**

#### Status definitions

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### Disclaimer

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, unless otherwise stated.

© Dialog Semiconductor GmbH. All rights reserved.

#### **RoHS Compliance**

Dialog Semiconductor complies to European Directive 2001/95/EC and from 2 January 2013 onwards to European Directive 2011/65/EU concerning Restriction of Hazardous Substances (RoHS/RoHS2). Dialog Semiconductor's statement on RoHS can be found on the customer portal https://support.diasemi.com/. RoHS certificates from our suppliers are available on request.

#### **Contacting Dialog Semiconductor**

Germany Headquarters Dialog Semiconductor GmbH Phone: +49 7021 805-0

United Kingdom Dialog Semiconductor (UK) Ltd Phone: +44 1793 757700

#### The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822

Email: enquiry@diasemi.com Application note North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

#### Japan Dialog Semiconductor K. K. Phone: +81 3 5425 4567

Taiwan

Dialog Semiconductor Taiwan Phone: +886 281 786 222

Web site: www.dialog-semiconductor.com Revision 1.2

#### Singapore

Dialog Semiconductor Singapore Phone: +65 64 849929

China

Dialog Semiconductor China Phone: +86 21 5178 2561

Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8291

25-Apr-2018