# Application Note Extending the SLG59M1693C's Maximum Operating Current Range

**AN-CM-240**

#### **Abstract**

This application note shows how to extend the SLG59M1693C's maximum operating current range.

#### **Contents**

| Ab                                                                        | ostract                                                                                                            | 1      |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------|

| Сс                                                                        | ontents                                                                                                            | 2      |

| Fiç                                                                       | gures                                                                                                              | 2      |

| 1                                                                         | Terms and Definitions                                                                                              | 3      |

| 2                                                                         | References                                                                                                         | 3      |

| 3                                                                         | Introduction                                                                                                       | 4      |

| 4                                                                         | Using Two SLG59M1693Cs in Parallel                                                                                 | 4      |

| 5                                                                         | Conclusions                                                                                                        | 7      |

| Re                                                                        | evision History                                                                                                    | 8      |

|                                                                           |                                                                                                                    |        |

| Fi                                                                        | igures                                                                                                             |        |

| Figure 1: Schematic Layout of Connecting Two SLG59M1693C IPSs in Parallel |                                                                                                                    |        |

| Fig                                                                       | gure 2: RDS <sub>ON</sub> vs. Temperature and V <sub>IN</sub> gure 3: PCB Layout for Using SLG59M1693C in Parallel | 5<br>5 |

| _                                                                         | gure 4: Turn on Operation Waveform for VIN = 2 V, CLOAD = 0.1 $\mu$ F, RLOAD = 1 $\Omega$                          |        |

| Fic                                                                       | rure 5: Turn on Operation Waveform for VIN = 0.8 V CLOAD = 0.1 uF RLOAD = 0.4 O                                    | 6      |

2 of 9

#### 1 Terms and Definitions

IPS Integrated Power Switch

#### 2 References

[1] SLG59M1693C, Datasheet, Dialog Semiconductor

#### 3 Introduction

Some applications require an IPS to deliver currents higher than 1 A. One way to address this requirement is to use an integrated power switch with higher current capability. However, such a part may occupy more PCB area or consume more power than optimal for the desired current rating. Another way to obtain higher current capability is to parallel two IPSs.

### 4 Using Two SLG59M1693Cs in Parallel

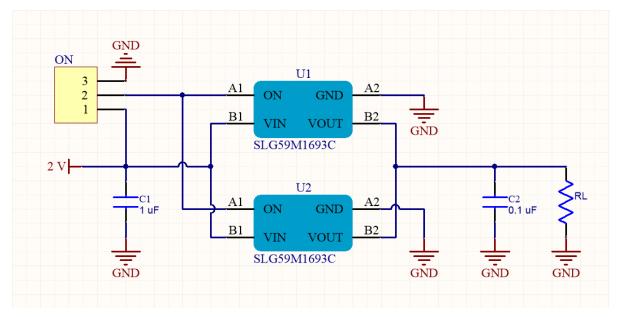

Parallel arrangement (Figure 1) divides the current between each IPS accordingly to its RDSon.

Figure 1: Schematic Layout of Connecting Two SLG59M1693C IPSs in Parallel

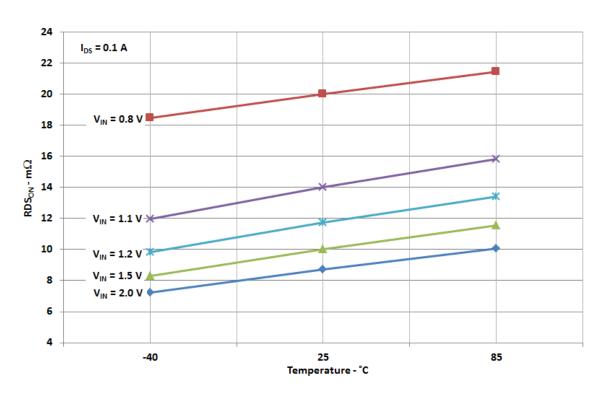

Using two IPSs in parallel lowers the overall RDS $_{ON}$  while maintaining low current consumption when ON, for any applications up to 2 A. A typical RDS $_{ON}$  vs. Temperature and V $_{IN}$  for this configuration is illustrated in Figure 2.

Figure 2: RDS<sub>ON</sub> vs. Temperature and V<sub>IN</sub>

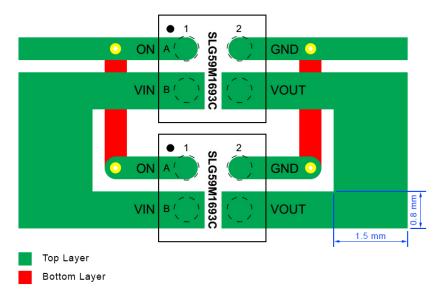

All PCB traces have the elements of resistance, capacitance and inductance. If there were a difference in path length from the voltage source to the IPSs pads, this delta trace length would create a current imbalance. In this case, the PCB layout should be designed properly to minimize parasitic impedance and especially parasitic inductance on  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  pins. Excess trace inductance may cause a delay effect during on/off operation. Figure 3 shows a recommended PCB layout for applications using two SLG59M1693Cs in parallel.

Figure 3: PCB Layout for Using SLG59M1693C in Parallel

Application Note Revision 1.0 22-Mar-2018

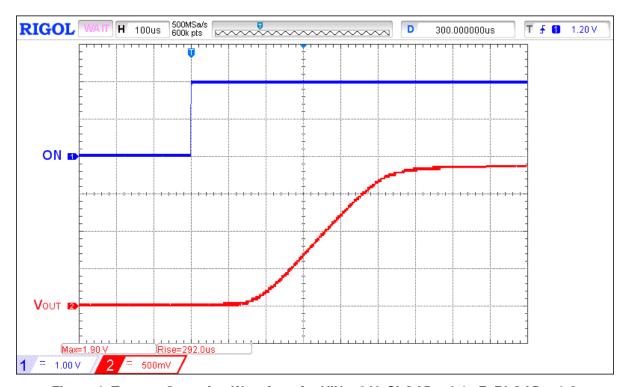

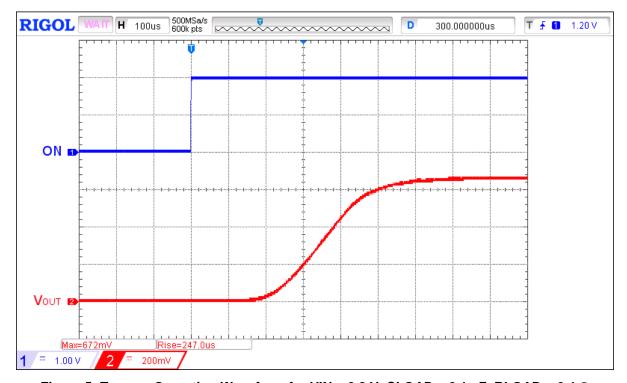

Typical operational waveforms of this two IPS solution are illustrated in Figure 4 and Figure 5.

Figure 4: Turn on Operation Waveform for VIN = 2 V, CLOAD = 0.1  $\mu$ F, RLOAD = 1  $\Omega$

Figure 5: Turn on Operation Waveform for VIN = 0.8 V, CLOAD = 0.1  $\mu$ F, RLOAD = 0.4  $\Omega$

#### 5 Conclusions

Using SLG59M1693Cs in parallel lowers the overall RDS $_{\rm ON}$ , but current consumption when on still remains low. The difference in path length from the voltage source to the IPSs pads may create a current imbalance, so the recommended PCB layout is presented.

## **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 22-Mar-2018 | Initial Version |

#### **Status Definitions**

| Status               | Definition                                                                                                                   |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| DRAFT                | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |  |

| APPROVED or unmarked | The content of this document has been approved for publication.                                                              |  |

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.

© 2018 Dialog Semiconductor. All rights reserved.

## **Contacting Dialog Semiconductor**

United Kingdom (Headquarters)

Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822

Email:

enquiry@diasemi.com

North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

Japan

Dialog Semiconductor K. K. Phone: +81 3 5769 5100

Taiwan

Dialog Semiconductor Taiwan Phone: +886 281 786 222

Web site:

www.dialog-semiconductor.com

Cong

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8200 China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

China (Shanghai)

Dialog Semiconductor China Phone: +86 21 5424 9058

Application Note Revision 1.0 22-Mar-2018