**Company confidential**

# **Application note**

# DA9155M PCB Layout Recommendations

**AN-PM-074**

#### **Abstract**

This application note provides recommendations on how to place and route the DA9155M device, and guidance on the passive components needed for proper functioning of the system. Application developers should treat this document as a guideline, not as a hard requirement, since the target application may have different requirements.

**Company confidential**

# **Contents**

| Application note |                                          |                        |                                                             |    |  |  |  |  |  |  |

|------------------|------------------------------------------|------------------------|-------------------------------------------------------------|----|--|--|--|--|--|--|

| DA               | 9155N                                    | I PCB L                | ayout Recommendations                                       | 1  |  |  |  |  |  |  |

| ΑN               | -PM-0                                    | 74                     |                                                             | 1  |  |  |  |  |  |  |

| Αb               | stract                                   |                        |                                                             | 1  |  |  |  |  |  |  |

| Со               | ntents                                   | <b></b>                |                                                             | 2  |  |  |  |  |  |  |

|                  |                                          |                        |                                                             |    |  |  |  |  |  |  |

| 1                |                                          |                        | efinitions                                                  |    |  |  |  |  |  |  |

| 2                |                                          |                        |                                                             |    |  |  |  |  |  |  |

| -<br>3           |                                          |                        |                                                             |    |  |  |  |  |  |  |

| 4                |                                          |                        |                                                             |    |  |  |  |  |  |  |

| 4                | <b>Layo</b> 4.1                          |                        | mmendations5M package information                           |    |  |  |  |  |  |  |

|                  | 4.1                                      | 4.1.1                  | DA9155M pin description                                     |    |  |  |  |  |  |  |

|                  |                                          | 4.1.1                  | Package information                                         |    |  |  |  |  |  |  |

|                  | 4.2                                      |                        | onverter                                                    |    |  |  |  |  |  |  |

|                  | 4.2                                      | 4.2.1                  | DA9155M input                                               |    |  |  |  |  |  |  |

|                  |                                          | 422                    | Ground connections                                          |    |  |  |  |  |  |  |

|                  |                                          | 4.2.3                  | VLX routing                                                 |    |  |  |  |  |  |  |

|                  |                                          | 4.2.4                  | Buck output                                                 |    |  |  |  |  |  |  |

|                  |                                          | 4.2.5                  | Battery voltage sense                                       |    |  |  |  |  |  |  |

|                  | 4.3                                      | _                      | unication interfaces (I <sup>2</sup> C)                     |    |  |  |  |  |  |  |

|                  | 4.4                                      |                        | ignals                                                      |    |  |  |  |  |  |  |

| 5                |                                          |                        | tory                                                        |    |  |  |  |  |  |  |

| 3                | Kevis                                    | 1011 11151             | ю у                                                         | 1  |  |  |  |  |  |  |

|                  |                                          |                        |                                                             |    |  |  |  |  |  |  |

|                  |                                          |                        |                                                             |    |  |  |  |  |  |  |

| Fi               | gure                                     | S                      |                                                             |    |  |  |  |  |  |  |

| Fig              | ure 1:                                   | DA9155                 | iM schematic                                                | 3  |  |  |  |  |  |  |

| Fig              | ure 2:                                   | DA9155                 | M WLCSP package outline drawing                             | 6  |  |  |  |  |  |  |

|                  |                                          |                        | nents placement on Dialog's DA9155M Evaluation Board        |    |  |  |  |  |  |  |

| Fig<br>Fig       | ure 4:                                   | Top lave               | nended input capacitor placement and routinger power ground | (  |  |  |  |  |  |  |

|                  |                                          |                        | yer 3 showing PGND and AGND                                 |    |  |  |  |  |  |  |

|                  |                                          |                        | yer 4 showing PGND and AGND                                 |    |  |  |  |  |  |  |

|                  | Figure 8: VLX pattern at top layer1      |                        |                                                             |    |  |  |  |  |  |  |

|                  |                                          |                        | tern at layer 2                                             |    |  |  |  |  |  |  |

|                  |                                          |                        | LC filter placement                                         |    |  |  |  |  |  |  |

|                  |                                          |                        | / voltage sense line routing/ / voltage sense routing       |    |  |  |  |  |  |  |

| i iy<br>Fia      | ure 13                                   | : I <sup>2</sup> C (SE | DA, SCL) interface lines                                    | 14 |  |  |  |  |  |  |

| 9                | igure 13: 1 C (SDA, SCL) interface lines |                        |                                                             |    |  |  |  |  |  |  |

**Company confidential**

#### 1 Terms and definitions

GPIO General Purpose Input/Output

PCB Printed Circuit Board

TH Through-Hole

WLCSP Wafer level chip scale package

WLP Wafer level packaging

#### 2 References

1. DA9155M Datasheet, Dialog Semiconductor

#### 3 Introduction

DA9155M is a slave charger that extends the current capability of an existing charging solution. It provides a regulated output current in the constant current phase of charging.

The DA9155M features a Buck converter capable of 2500 mA output current. The Buck regulates the output current with ±5 % accuracy. Current sensing is performed with a fully integrated circuit.

The input voltage range of 4.5 V to 13.5 V makes the DA9155M suitable to be powered from USB and high voltage travel adaptors. The output current limit is configurable in the range of 400 mA to 2500 mA in 10 mA steps.

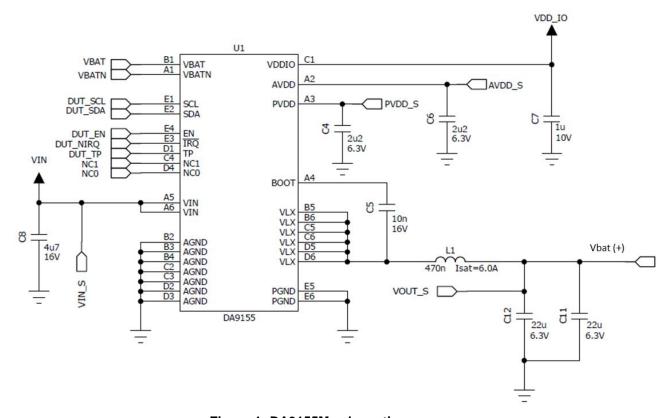

The basic recommended components and connections for DA9155M are shown in Figure 1. DA9155M components and specifications for Capacitors are shown in Table 1 and for inductor in Table 2.

Figure 1: DA9155M schematic

**Company confidential**

**Table 1: Capacitors**

| Reference              | Quantity | Value  | Size (mm) | Temp char. | Tol.   | Voltage rating (V) |

|------------------------|----------|--------|-----------|------------|--------|--------------------|

| Buck input bypass cap  | 1        | 4.7 μF | 1608      | X5R        | ±20 %  | 16                 |

| Buck output bypass cap | 2        | 22 µF  | 1608      | X5R        | ±20 %  | 6.3                |

|                        |          |        |           |            |        | 16                 |

| Buck bootstrap cap     | 1        | 10 nF  | 1005      | X7R        | ±10 %  | (min 6.3)          |

| AVDD output bypass cap | 1        | 2.2 µF | 1005      | X5R        | ±20 %  | 6.3                |

| PVDD output bypass cap | 1        | 2.2 µF | 1005      | X5R        | ± 20 % | 6.3                |

#### **Table 2: Inductor**

| Reference            | Value (µH) | ISAT (A) | IRMS (A) | DCR (typ. [mΩ]) | Size (L×W×H [mm]) |

|----------------------|------------|----------|----------|-----------------|-------------------|

| Buck output inductor | 0.47       | 6        | 4.5      | 24              | 2.5×2.0×1.0       |

# 4 Layout recommendations

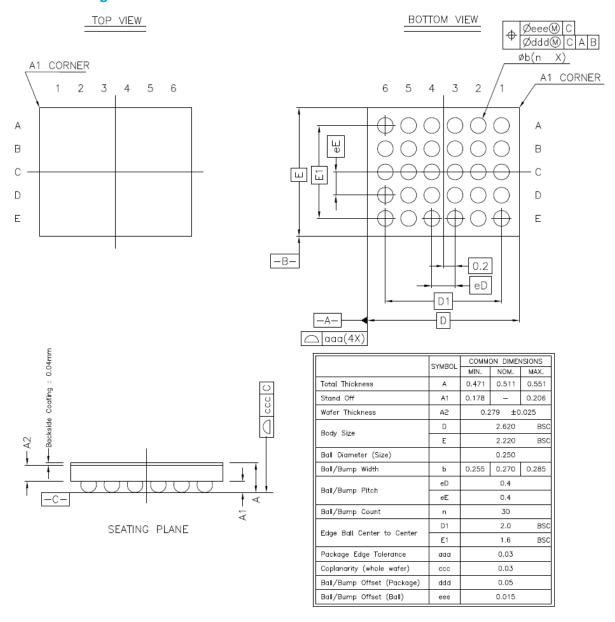

DA9155M is packaged in a 30-pin WL-CSP device with a 0.4 mm pitch, 30 bumps WLP, 2.6 mm x 2.2 mm, 0.5 mm height.

At least a four-layer PCB stack-up should be used for best PCB layout design. However, the number of routing layers and other PCB parameters are also determined by the other devices in the system.

This document references Dialog's DA9155M Evaluation Board, which is a six-layer PCB stack-up, as an example to describe a recommended PCB layout design.

This document is divided into the following sections:

- Package information (section 4.1)

- Buck converter (section 4.2)

- Communication interfaces (section 4.3)

- GPIOs and control signals (section 4.4)

**Company confidential**

# 4.1 DA9155M package information

# 4.1.1 DA9155M pin description

Table 3: Pin description

| Pin                                | Name  | Туре | Description                                          |

|------------------------------------|-------|------|------------------------------------------------------|

| C1                                 | VDDIO | PS   | IO supply                                            |

| B2, B3,<br>B4, C2,<br>C3,D2,<br>D3 | AGND  | GND  | Analog ground                                        |

| A2                                 | AVDD  | AIO  | Internal supply                                      |

| A3                                 | PVDD  | AIO  | Internal supply                                      |

| E2                                 | SDA   | DIO  | Data signal of the 2-wire interface (GPIO)           |

| E1                                 | SCL   | DI   | Clock signal of the 2-wire interface (GPIO)          |

| E4                                 | EN    | DI   | Control signal for the output current/voltage (GPIO) |

| E3                                 | nIRQ  | DO   | Interrupt signal to host processor (GPIO)            |

| A5, A6                             | VIN   | PS   | Input supply                                         |

| B5, B6,<br>C5, C6,<br>D5, D6       | VLX   | АО   | Switching node of buck                               |

| A4                                 | воот  | AIO  | Supply of the high-side driver                       |

| B1                                 | VBAT  | Al   | Battery voltage sense, positive terminal             |

| A1                                 | VBATN | Al   | Battery voltage sense, negative terminal             |

| E5, E6                             | PGND  | GND  | Power grounds of the buck, digital ground            |

| D1                                 | TP    | DIO  | Test pin                                             |

| C4, D4                             | NC    |      | Not connected.                                       |

#### **Table 4: Pin type definition**

| Pin type | Description                     | Pin type | Description                   |

|----------|---------------------------------|----------|-------------------------------|

| DI       | Digital Input                   | Al       | Analog Input                  |

| DO       | Digital Output                  | AO       | Analog Output                 |

| DIO      | Digital Input/Output            | AIO      | Analog Input/Output           |

| DIOD     | Digital Input/Output open Drain | BP       | Backdrive Protection          |

| PU       | Fixed pull-up resistor          | SPU      | Switchable pull-up resistor   |

| PD       | Fixed pull-down resistor        | SPD      | Switchable pull-down resistor |

#### **Company confidential**

# 4.1.2 Package information

Figure 2: DA9155M WLCSP package outline drawing

**Company confidential**

# 4.2 Buck converter

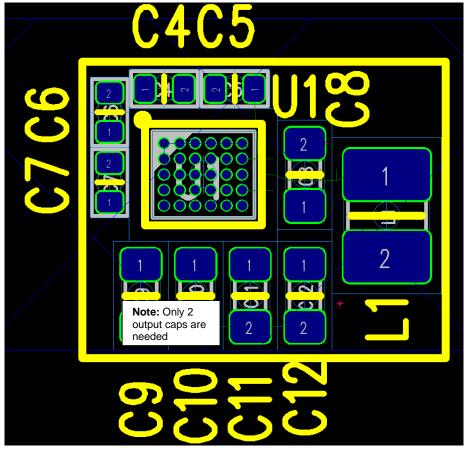

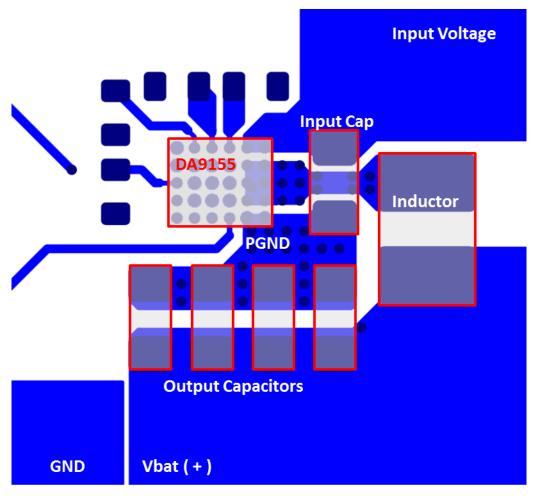

Figure 3 provides a guideline for component placement. The reference designators used in this section match the schematic shown in Figure 1.

Figure 3: Components placement on Dialog's DA9155M Evaluation Board

**Company confidential**

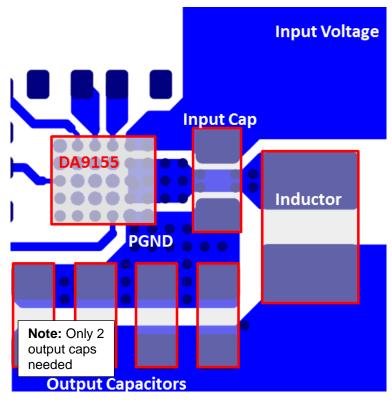

#### 4.2.1 **DA9155M** input

In a Buck converter layout, input capacitor location is critical. The input capacitor needs to be located as close as possible to the device's input and power GND pins. The step-down input bypass capacitors are the most critical components because they carry discontinuous currents with a high rate of change (di/dt). For the DA9155M layout design, the input capacitor for the Buck converter should be placed as close as possible to the VIN and PGND pins, and **on the same layer as the DA9155M device**. The traces between the input capacitor pads and device balls need to be as short as possible to minimise parasitic inductance. Placing the input capacitor on the opposite side of the PCB is not ideal because the vias that are necessary to connect the two halves of the PCB add inductance to this critical path.

If multiple layers are used, Dialog recommends using at least four TH vias (or eight micro-vias) to connect the input voltage (VIN) between layers and to minimise trace impedance. Also ensure that there is a sufficient number of vias to connect the input capacitor GND to the inner layer GND plane.

It is also recommended to place a 1 µF decoupling capacitor on VDD\_IO line close to the DA9155M.

Figure 4 shows the input capacitor placement and routing recommendation.

Figure 4: Recommended input capacitor placement and routing

#### 4.2.2 Ground connections

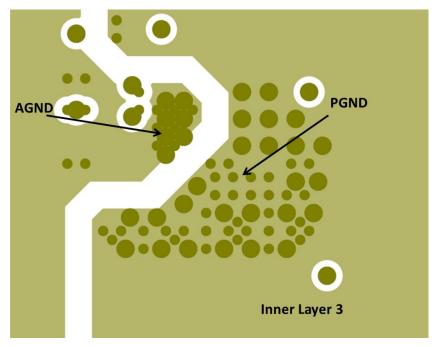

Special care should be taken with ground connections because of the high performance requirements of the DA9155M.

The Buck converter PGND terminals should be connected together on the same layer as these are noisy power GNDs, and they should not be connected directly to any analog GND (for example, AGND) on the same layer.

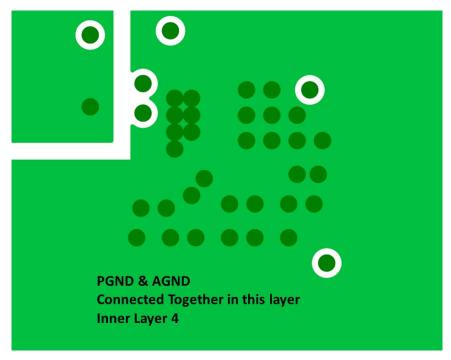

It is recommended to connect power GND and analog GND together at a solid internal GND plane. It is best practice to isolate the power GND (noisy GND) from the analog GND (quiet GND) and to connect them at a single point close to the device. In addition, the PCB layout should minimise the line impedance of PGND pins and output capacitors GND connections by using as many vias as possible. This will also improve the heat dissipation.

**Company confidential**

#### NOTE

It is always recommended to use copper plugged vias in order to achieve the minimum parasitic via impedance, and best thermal performance.

Layer 3 can be used as a common GND plane. The common GND plane on Layer 3 also acts as a shield to protect noise-sensitive signal lines (for example, feedback lines) on Layer 4 and below from switching-noise interference. Also, connecting the less noisy output capacitor GND (instead of input capacitor GND) to common GND is preferable.

Examples of how to connect the GND terminals on Dialog's DA9155M Evaluation Board is illustrated in Figure 5, Figure 6, and Figure 7.

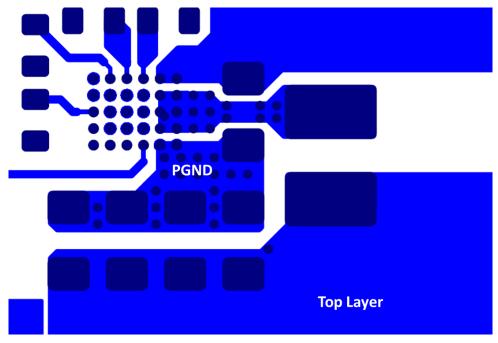

Figure 5: Top layer power ground

Figure 6: Inner layer 3 showing PGND and AGND

**Company confidential**

Figure 7: Inner layer 4 showing PGND and AGND

**Company confidential**

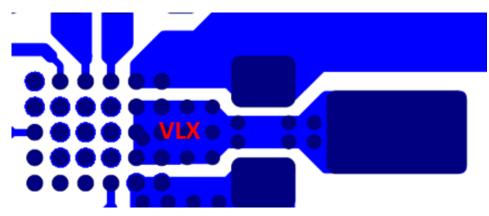

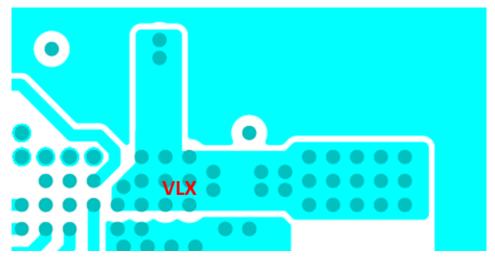

#### 4.2.3 VLX routing

Switch node/VLX node traces (traces between VLX pin and the output inductor) need to be kept as short as possible since this node generates switching noise, and this can interfere with Buck converter stability. High current will flow through this trace and the minimum trace width for this VLX node must be considered.

Multiple layers may be preferable for VLX node traces. Also, ensure that there are enough vias (0.5 A per micro-via) to deliver the current.

Figure 8 and Figure 9 show the VLX node pattern on Dialog's DA9155M Evaluation Board.

Figure 8: VLX pattern at top layer

Figure 9: VLX pattern at layer 2

**Company confidential**

#### 4.2.4 Buck output

Output capacitors should be placed as close as possible to the load. Do not split the output capacitors into local capacitors (close to the output inductor) and remote capacitors (close to the load) as this may affect the stability of the Buck converter.

However, minimising the distance (thus minimising the line impedance) from the output inductors to the output capacitors (the load) is also important since it directly affects the efficiency and load transient response performance of the Buck converter. Care must be taken regarding the size of the output traces since the output peak current can be up to 2500 mA for DA9155M.

It is best practice to transfer the output current at the top layer directly without using any vias. This will give the best performance in terms of efficiency and load transient response performance.

Figure 10 shows an example of inductor and capacitor placement based on Dialog's DA9155M Evaluation Board.

Figure 10: Output LC filter placement

**Company confidential**

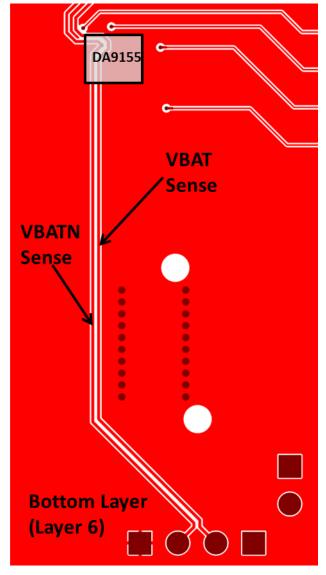

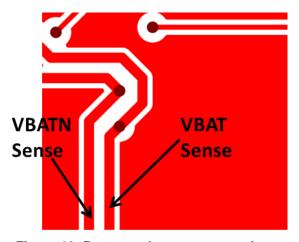

#### 4.2.5 Battery voltage sense

It is recommended to route the positive battery voltage sense (VBAT) and negative battery voltage sense (VBATN) as a differential pair to the battery connecting terminals, far from any noise source (for example, output inductors, VLX node, and such). This will help achieve the best voltage accuracy.

Also, ensure that the voltage sense lines are not overlapping any noisy node traces (for example, the VLX node trace) without an isolation plane layer in between. Assuming that DA9155M is assembled on the top layer, it is recommended to route the sense lines on layer 4 or below when the traces are near to the IC and/or the switch node areas.

#### NOTE

The negative battery voltage sense trace is at ground potential and care should be taken not to connect any part of the trace to the ground plane.

Figure 11 and Figure 12 show an example of the battery voltage sense routing on Dialog's DA9155M Evaluation Board.

Figure 11: Battery voltage sense line routing

**Company confidential**

Figure 12: Battery voltage sense routing

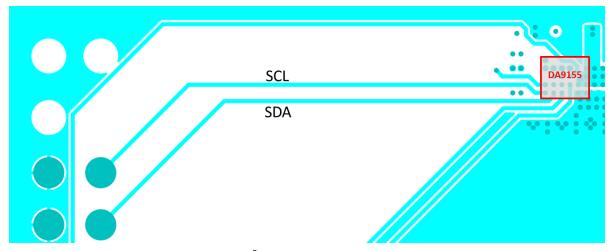

# 4.3 Communication interfaces (I<sup>2</sup>C)

There are no firm rules regarding the interface routing strategy. All of the signals are digital and are immune to various kinds of noise.

Care must be taken regarding the noise produced by the interface signal in order to avoid coupling to the sensitive analog references and feedbacks. The routing layer is not critical, but using the bottom or top layer is recommended.

Figure 13: I<sup>2</sup>C (SDA, SCL) interface lines

#### 4.4 **GPIO** signals

Generally GPIOs have the lowest routing priority. Any layer can be used for routing these signals.

**Company confidential**

# 5 Revision history

| Revision | Date       | Description     |

|----------|------------|-----------------|

| 1.0      | 12/08/2015 | Initial version |

|          |            |                 |

|          |            |                 |

|          |            |                 |

Company confidential

#### **Status definitions**

| Status               | Definition                                                                                                                   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED or unmarked | The content of this document has been approved for publication.                                                              |

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, unless otherwise stated.

© Dialog Semiconductor GmbH. All rights reserved.

#### **RoHS Compliance**

Dialog Semiconductor complies to European Directive 2001/95/EC and from 2 January 2013 onwards to European Directive 2011/65/EU concerning Restriction of Hazardous Substances (RoHS/RoHS2).

Dialog Semiconductor's statement on RoHS can be found on the customer portal <a href="https://support.diasemi.com/">https://support.diasemi.com/</a>. RoHS certificates from our suppliers are available on request.

# **Contacting Dialog Semiconductor**

Germany Headquarters

Dialog Semiconductor GmbH Phone: +49 7021 805-0

United Kingdom

Dialog Semiconductor (UK) Ltd Phone: +44 1793 757700

The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822

Email

enquiry@diasemi.com

North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

Japan

Dialog Semiconductor K. K. Phone: +81 3 5425 4567

Taiwan

Dialog Semiconductor Taiwan Phone: +886 281 786 222

Web site:

www.dialog-semiconductor.com

Singapore

Dialog Semiconductor Singapore Phone: +65 64 849929

China

Dialog Semiconductor China Phone: +86 21 5178 2561

Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8291

Application note

Revision 1.0

08-Dec-2015