# Abstract

This User Guide provides recommendations for routing USB signals to Dialog BCID ICs

# Contents

| Ab  | stract             | 1 |

|-----|--------------------|---|

| Co  | ntents             | 2 |

| Fig | ures               | 2 |

| -   | Introduction       |   |

|     | General Routing    |   |

| 3   | DP/DM routing      | 3 |

| 4   | SLG5554x Placement | 5 |

# **Figures**

| Figure 1   | races routing | <br>4  |

|------------|---------------|--------|

| i iguic i. | acco routing  | <br>Τ. |

# **1** Introduction

This document provides guidelines for some common questions about integrating a SLG5554x highspeed USB power switch and controller onto a PCB. It is not an exhaustively complete list of PCB design rules but only recommendations.

USB requires two signals in a channel. For most data transfers, when one signal is high, the other is low. This is known as a differential pair. USB has specific shielding, signal and power conductor requirements. These requirements are identified in the USB 2.0 specification.

# 2 General Routing

Because of the high frequencies associated with the USB, a printed circuit board with at least four layers is recommended; two signal layers separated by a ground and power layer. The majority of signal traces should run on a single layer. Immediately next to this layer should be the GND plane, which is solid with no cuts. Avoid running signal traces across a split in the ground or power plane. When running across split planes is unavoidable, sufficient decoupling must be used. Minimizing the number of signal vias reduces EMI by reducing inductance at high frequencies.

- Place the BCID and major components on the un-routed board first.

- Route the high-speed USB differential signals with minimum trace lengths.

- Route the high-speed USB signals using a minimum of vias and corners. This reduces signal reflections and impedance changes.

- Route the high-speed USB signals on the plane closest to the ground plane, whenever possible.

- When it becomes necessary to turn 90°, use two 45° turns or an arc instead of making a single 90° turn. This reduces reflections on the signal traces by minimizing impedance discontinuities.

- Do not route USB traces under or near crystals, oscillators, clock signal generators, switching regulators, mounting holes, magnetic devices or IC's that use or duplicate clock signals.

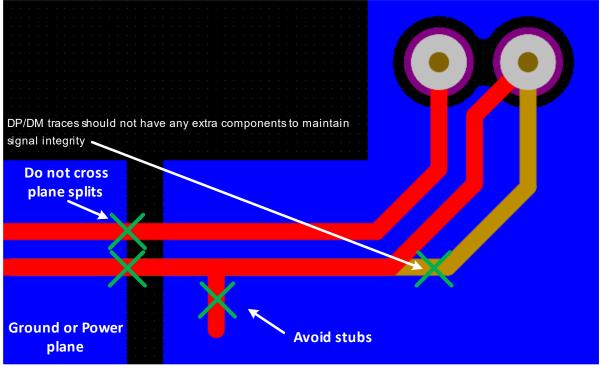

- Avoid stubs on the high-speed USB signals because they cause signal reflections. If a stub is unavoidable, then the stub should be less than 200 mils.

- Route all high-speed USB signal traces over continuous planes (VCC or GND), with no interruptions.

- Avoid crossing over anti-etch, commonly found with plane splits.

## 3 **DP/DM routing**

At the PCB, the USB connector consists of 4 main signals: VBUS (+5 V power), Ground and DP and DM. DP and DM are the differential pair. The signal swing during high-speed operation on the DP/DM lines is relatively small (400 mV ± 10%), so any differential noise picked up on the twisted pair can affect the received signal. When the DP/DM traces do not have any shielding, the traces tend to behave like an antenna and picks up noise generated by the surrounding components in the environment. So these two signals must be closely matched with the following characteristics:

- Place the BCID as close as possible to the USB 2.0 connector.

- Both DP and DM signals must travel the same distance. If one trace ends up longer, then the timing of the signals can be adversely affected and cause data errors.

- The impedance of the twisted pair cabling must be matched on the PCB in order to minimize signal reflections. USB signals are 90 Ω differential to each other / 45 Ω each to Signal Ground.

**Layout Guidelines**

**Revision 1.0**

Most modern PCB layout software can be configured to route both of these signals together with these characteristics.

- When adding components such as transient voltage protection or additional capacitance for edge rate control, the DP and DM signals should not have any stubs in order to minimize signal reflections.

- Route DP/DM traces close together for noise rejection on differential signals, parallel to each other and within two mils in length of each other (start the measurement at the chip package boundary, not to the balls or pins).

- With DP and DM being controlled impedance, they should consistently run over the USB Signal Ground plane. There should not be any splits in the plane directly under DP and DM.

- The DP and DM signals should be made as short as possible.

- DP/DM traces should not have any extra components to maintain signal integrity. For example, traces cannot be routed to two USB connectors

- General design practices: Keep noisy sources away from the USB signals; avoid right angles;

When a via must be used, increase the clearance size around it to minimize its capacitance. Each via introduces discontinuities in the signal's transmission line and increases the chance of picking up interference from the other layers of the board. Be careful when designing test points on twisted pair lines; through-hole pins are not recommended.

Do not overlap planes that do not reference each other. For example, do not overlap a digital power plane with an analog power plane as this produces a capacitance between the overlapping areas that could pass RF emissions from one plane to the other.

Switching power regulators are a source of noise and can cause noise coupling if placed close to sensitive areas on a circuit board. Therefore, the switching power regulator should be kept away from the DP/DM signals, the external clock crystal (or clock oscillator), and the BCID.

| Figure 1. | DM/DP | traces | routing |

|-----------|-------|--------|---------|

|-----------|-------|--------|---------|

| Layout Guidelines | Revision 1.0 | 28-05-2020 |

|-------------------|--------------|------------|

|                   |              |            |

# 4 SLG5554x Placement

Place the SLG5554x close to the USB connector. Connect the exposed pad to the GND pin and the system ground plane using an array of vias. Connect a 0.1  $\mu$ F or greater ceramic capacitor from IN to GND as close to the device as possible. Route DP-OUT/DM-OUT, DP-IN/DM-IN traces according to recommendations above. Minimize the use of vias in the high-speed data lines. Ensure that the reference plane is void of cuts or splits above the differential pairs to prevent impedance discontinuities. Place the components for CTL1, CTL2, CTL3, ILIM\_SEL, ILIM\_H, ILIM\_L, FAULT# and STATUS# configuration as close as possible to corresponding pads.

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### Disclaimer

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.

© 2020 Dialog Semiconductor. All rights reserved.

# **Contacting Dialog Semiconductor**

United Kingdom (Headquarters) Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

Germany Dialog Semiconductor GmbH

Phone: +49 7021 805-0 The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822

Email: enquiry@diasemi.com

#### North America

*Dialog Semiconductor Inc.* Phone: +1 408 845 8500

#### Japan

Dialog Semiconductor K. K. Phone: +81 3 5769 5100

#### Taiwan

Dialog Semiconductor Taiwan Phone: +886 281 786 222 Web site: www.dialog-semiconductor.com

#### Hong Kong

Korea

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

Dialog Semiconductor Korea

Phone: +82 2 3469 8200

## China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

China (Shanghai) Dialog Semiconductor China Phone: +86 21 5424 9058

### **Layout Guidelines**

#### 28-05-2020